芯片,是近一直牵动着中国科技行业的核心技术,5G,将是引领科技未来十年以上发展的基础通信技术,中国更是将其纳入了未来十年50万亿新基建的七大板块之一。自然,5G芯片的行业发展及技术将会是这场未来十年以上通信时代和基础设施建设的。

2020年6月28日,在《电子工程专辑》、《电子技术设计》、《电子商情》三大媒体联合举办的“2020年中国IC领袖峰会”上,中兴资深SoC芯片副总邹飞从5G芯片产业发展趋势、5G无线芯片设计挑战、5G无线芯片关键技术等方面阐述了5G芯片行业发展趋势及技术挑战。

5G芯片产业发展趋势

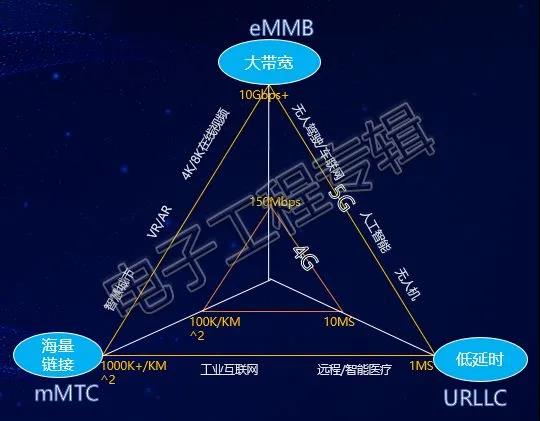

5G能给我们生活带来什么呢?2020的全球疫情期间,经过媒体和电视可以看到,专家通过高清视频,参与疫情的分析和诊断,这就是5G商用一个场景。远程和智能医疗,都是基于5G的大带宽和低延迟技术。具体来讲,5G跟4G比有哪些大改变呢?

首先5G将通讯的帧格式做了重大调整,以前帧格式都是按10毫秒,现在调整到一个数量级,调整到1毫秒。传输速率由原来的150Mbps,到10Gbps。

为了适应万物互联或者是海量的互联,5G设计了mMTC支持海量连接。在5G里面有eMMB,mMTC,URLLC三种应用场景,未来适应这三种场景,采用了网络切片技术,在同一套网络上可以并行运营三种业务,5G因为低延迟和大带宽,为后面的人工智能,包括无人驾驶,VR,AR提供了很好的场景落地。

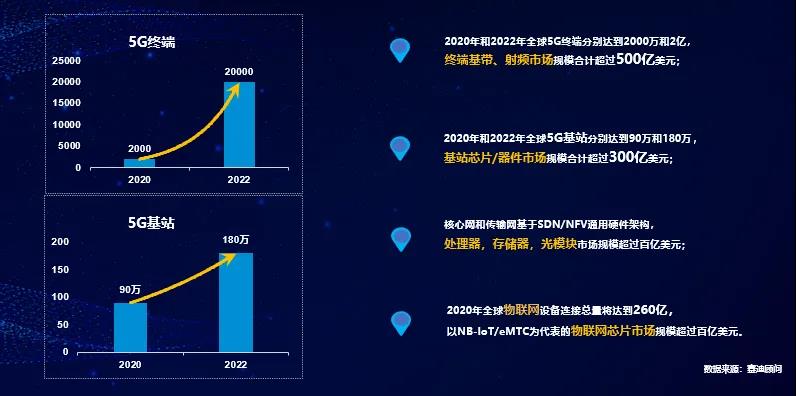

现在VR,AR,其实在应用中多半都是连一根数据线,如果5G普及了这根数据线不需要了,这会极大提高用户体验。这是相关媒体对未来5G发展阐述的预测,预计到2020年,5G终端基带与射频市场将合作,可能会超过5千亿美金。到2020年全球基站芯片和器件市场可能会超过三百亿美金,核心网这块有可能会超过上百亿美金,物联网这块,以NB-IoT和eMTC为代表物联网芯片市场也可能会超过上百亿。

看一下半导体产业在2018年,进入2019年这个期间,在5G商用之前实际上有一个下降的趋势。但是在5G商用和AI物联网,汽车智能化推动下,其实在2019年开始出现一个反弹,另外一个趋势,随着技术演进,芯片占比和营收占比会越来越高。

5G无线芯片设计挑战

芯片其实就是5G发展的一个基石,某通讯厂商在5G初始发展过程中并不是以(ASIC)为基石,近技术测试,包括成本方面都不占,在国内折戟了。现在他们公司也在将FPGA方案调整为ASIC方案。中兴微电子,特别是系统端市场已经投入了20几年了,我们涉及的主要市场还是系统测试像接入网和承载网,包括后面核心网,我们在接入网,有多模基态芯片和射频芯片,包括有OTN,包括在光传输这块有600G的OTN芯片,100G的光模块DS芯片,在路由交换这块,我们有8.8T的分组交换套片,2.4T网络处理器及以太网交换机芯片。

在终端这块可能投入稍微小一些,有NB-IoT物联网的芯片,还有家庭网光芯片,还有8K高清多媒体芯片。5G芯片设计挑战大概什么样呢?我们以5G基站为例,5G时代通道数有8倍,5G时代变成了64T64R,处理的单载波带宽由原来20兆变为100兆,甚到高频时候到400兆,流数原来4-8,可能变成后面的16-32,这个处理能力基本上都是5倍,20倍的。

所以在芯片集成度,性能方面来说,5G芯片都需要大幅。同时要考虑到,特别是AAU这块,它的散热,它是得靠自然散热,没有办法添加空调或者风扇,所以功耗不能无限,或者说增加特别多。所以功耗这块是我们必须要考虑的,另外灵活性,因为5G协议实际上是在不停演进,我们不是做一款芯片就不支持协议的演进,所以我们在灵活性上面也是有诉求的。

5G这么多需求,到芯片实现商来说,可能芯片能实现更高的性能,更高的功耗?还有超大规模,还有高集成度,高性能来说,因为我们的算力是有20倍,所以说我们对于CPU,DSP的要求是前所未有的提高。因为贷款增加,导致对外存,像DDR的贷款需求是大幅的,单靠增加DDR个数可能都没有办法满足我们的要求,我们得像HBM这种新技术进行演进,包括对外接口,像在4G时代对外接口可能就是200G够用了,但是到了5G时代,可能要达到数T,所以你的接口必须由原来的10G,25G,向50G,112G演进。由于性能提高,主频原来说可能都是几百兆,到了5G时代不说CPU,就说一些加速器可能都要到达1T,2T工作频率。

功耗这块,因为芯片规模变大,功耗从几十万,可能到几百万。所以功耗分析和低功耗是我们必须要去考虑的事情,超大规模带来另外一个问题就是如何实现。可能一个几十万,或者几千万芯片,不用考虑一些难度,但是到了几十亿就会遇到各种各样的瓶颈,比如顶层走线。未来应对这些挑战我们提出一些关键技术,因为做芯片,特别是我们做大规模SOC芯片,IP永远是我们需要讨论的,比如5G高速的ADDA,相对于4G来说,无论是采样频率,还是采样带宽都是大幅的,所以ADDA的性能也需要得到大幅的。因为我们需要计算或者运算的带宽、流量也是很大,所以我们对DSP、CPU都是有严苛的要求。

因为需求都是几倍的增加,所以我们对架构必须要,特别是架构的平台设计。因为设计一个架构没有平台进行落地,你没有办法验证这个架构是否符合你的设计预期。关于林火行,因为我们设生产的芯片或者做的芯片不可能只为了应对一种场景或者不为将来做更多的事情,因此灵活性是我们必须要保证的。另外我们处理的业务可能千奇百怪,所以不可能光CPU或者DSP打天下,这可能需要更多的异构。

软硬件的合理划分我就不多说了,因为硬件的速度永远快于软件的速度,但硬件有一定的局限性,所以在做架构设计的时候软硬件划分也是*重要的。低功耗到了几十瓦或者功耗特别大的芯片,这也是*重要的,对于低功耗我们有多种手段,从架构、算法就开始着手考虑这些事情。在实践上面有多电源、电源关断这也是我们必须要考虑的,像传统的多频点,包括后续的AVS、DVS这种技术。

物理实验这一块也是难点(大芯片布局),因为我们现在芯片规模特别庞大,可能模块由原来的十几、几十变成上百,所以这个芯片怎么布局也是特别重要的。

关于先进的话,目前我们的规模可能达到几十亿或者上百亿,所以你不采用先进无论是成本,还是功耗,这方面都是完全没有办法实现的事情。因为规模机器庞大,如果读了时钟还用传统的CTS或者传统的分指树,这基本上是不可能完成的任务。关于封装技术,现在随着的演进、放缓,还有数字跟模拟,特别是模拟的演进更缓慢,所以先进封装包括MSF或者后期的封装也是未来发展的趋势。

5G无线芯片关键技术

5G芯片涉及关键应对技术有以下几个方面:

关键IP

• 高速SERDES

• 高速ADC/DAC

• 高性能DSP

• 高性能CPU

架构创新

• 架构设计平台

• 灵活互联架构

• 异构设计

• 合理软硬件划分

低功耗技术

• 系统架构及算法优化

• 多电源域/电源关断

• Clock gating

• 多时钟/多频点方案

• AVS/DVFS低功耗方案

物理实现技术

• 大芯片布局技术

• 先进技术

• 结构化时钟树

• 先进封装技术

其根本目的是要实现更高效、低成本、低功耗、高性能关键技术。

对IP来说,要求的性能永远是更强的,主频肯定是越高越好,面积肯定是越小越好。内存不一定是越大越好,能耗肯定是越低越好,但市面上能选择的CPU种类还是比较多的,它的功耗、性能不是完全等价的,所以在选型这一块需要做很多的评估工作。一个的架构一定要有一个高效,并且能量化的手段,那这个架构是满足我们设计需求的。实际上VS是一个不错的选择,目前GTEES平台已经创立。我们会对自研加速器进行一些建模,为什么要进行建模?在前期你的代码可能是没有的,就算有,反证时间可能是没有办法想象的,建模好处就是能快速进行一个反证,验证这个平台架构是否合理,或者架构瓶颈和缺陷在哪里。另外还有一个好处,在硬件好的时候,能为软件提供一个调试平台,这样加快芯片的商用,为什么现在的5G商用落地这么快,无论GT还是华为,在芯片推出来的半年以内芯片规模就能商用,就是依赖于各个厂家他们的仿真平台,可以做软硬件同步开发。

自研的算法IP,在5G协议里面常用一些IP基本上都已经通过自研,都有自己的模型。讲两个架构探索的方案,其实前期我们做了一个系统逻辑图,通过一些简单分析做了一个架构同一个架构进行建模,发现某些走线能进一步合并,通过优化获得了不错的收益,有20%多,面积了也接近20%。另外一个软硬件协同划分,以前都是软件直接调度,前期处理完,通知软件,软件再通知下级硬件,这种软件效率永远比硬件要低,这种效率到了5G,基本上没有办法满足要求,所以我们可以通过调整架构,硬件直接触发,这样把任务处理的时间大大压缩了,这个性能也就了,其实做ES仿真跟传统设计来看,仿真这块,或者建模这块占用时间会比以前看上去多很多。但是他可以加快后面代码实现,包括验证,你有仿真或者架构平台,对你后面的验证组织都会快很多。所以对整个项目总体来看,到终还是有10-20%的,时间的节省。

功耗,特别到的5G芯片,是芯片设计中重中之重。功耗设计或者功耗优化也是一直贯穿于整个设计流程之中的,架构设计,比如算法IP,从系统设计到架构设计包括,包括布局实现,包括量产。我们做了一个大概的评估,内部某一个5G基带芯片优化评估,从方案优化这块,大概优化出了20W,从独点运营的方案,因为我们未来追求算力,像DSP,未来达到某一个平点需要加压,否则在当前情况下是不可能做到的。

其实芯片上有很多其他模块可能不需要,可能他的频率没有那么高,或者代码分隔比较好能满足。我们会采用多电源,(英)跟代码分隔有关,这是代码一些优化。ABS是一个好技术,我们的量率肯定是有几种不同的标准。对LT这个时候通过功率电压来功耗,同时对SS片可以加压,这样我们做(英)的时候可以适当放松对它的要求。对LF来说通过降压可以控制功耗。

讲一下物理实验几个技术,这里我们做了一些实验,跟自己自研的,都不会特别差。所以对芯片设计,后面的实现,从项目经验来看,这块还是比较好的。物理实验另外一个技术就是Hfperscale,我们做了一个对比,随着规模越大服务器的需求也是下降的。现在芯片设计瓶颈,特别是高性能芯片设计瓶颈永远是存储速度跟不上我们的算力,所以说算力一体化架构也是未来的一个热点,可重构计算器,相当于我们为什么要提可重构?实际上我们的应用是千奇百怪的,或者是变化比较快的,如果能做到可重构,相当于我们可根据业务模型调整硬件处理流程,来达到匹配我们的预算。

新材料,新结构,晶体管持续微缩也是一个方向。封装也是近一个比较热门的技术,现在芯片演进速度在放缓的,包括模拟的芯片速度或者模拟IP速度远远跟不上数字,我们也可以考虑封装技术合封到一起,也是一种方向,包括后面,我们的3D封装,以后不用把芯片做的*巨大,可以拆成多个芯片设计,通过搭积木方式搭在一起,封装在一起。带宽能10倍,功耗也是有下降的。

邮箱:15236061639@163.com

QQ:60298351

微信:a18137798589

2025年是港股机器人板块规模化落地与盈利拐点并行的关键一年。据高工机器人不完全统计,优必选、越疆、

4月11日,宇树科技宣布H1机器人刷新人形机器人百米测试奔跑速度的世界纪录。视频显示,H1机器人在此

近日,全国首条年产能达万台级别的人形机器人自动化生产线正式启用,这意味着中国在人形机器人规模化制造领